Penyelesaian Soal 10.11

- Mengetahui bentuk rangkaian dan mensimulasikan pengaplikasian dari tugas soal pada software proteus.

- Dapat mensimulasikan rangkaian di aplikasi proteus

- Menyelesaikan tugas dari bapak darwinson

1. JK flip-flop

JK flip-flop merupakan flip flopyang dibangun berdasarkan pengembangan dari RS flip-flop. JK flip-flop sering diaplikasikan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). JK flip flop dalam penyebutanya di dunia digital sering di tulis dengan simbol JK -FF. Dalam artikel yang sedikit ini akan diuraikan cara membangun sebuah JK flip-flop.Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika DasarJK flip-flop merupakan flip flopyang dibangun berdasarkan pengembangan dari RS flip-flop. JK flip-flop sering diaplikasikan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). JK flip flop dalam penyebutanya di dunia digital sering di tulis dengan simbol JK -FF. Dalam artikel yang sedikit ini akan diuraikan cara membangun sebuah JK flip-flop

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

Read more at: https://elektronika-dasar.web.id/jk-flip-flop/

Copyright © Elektronika Dasar

2. Logic State

status logika Pengertian logis, benar atau salah, dari sinyal biner yang diberikan. Sinyal biner adalah sinyal digital yang hanya memiliki dua nilai yang valid. Dalam istilah fisik, pengertian logis dari sinyal biner ditentukan oleh level tegangan atau nilai arus sinyal, dan ini pada gilirannya ditentukan oleh teknologi perangkat. Dalam sirkuit TTL, misalnya, keadaan sebenarnya diwakili oleh logika 1, kira-kira sama dengan +5 volt pada garis sinyal; logika 0 kira-kira 0 volt. Tingkat tegangan antara 0 dan +5 volt dianggap tidak ditentukan.

Logic Probe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

Logic probe menggunakan dua lampu indikator led yang berbeda warna untuk membedakan keluaran High atau Low. Yang umum dipakai yaitu LED warna merah untuk menandakan output berlogika HIGH (1) dan warna hijau untuk menandakan output berlogika LOW(0).

4. IC 10135

JK flip-flop merupakan flip flopyang dibangun berdasarkan pengembangan dari RS flip-flop. JK flip-flop sering diaplikasikan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter)

Konfigurasi pin IC 10135

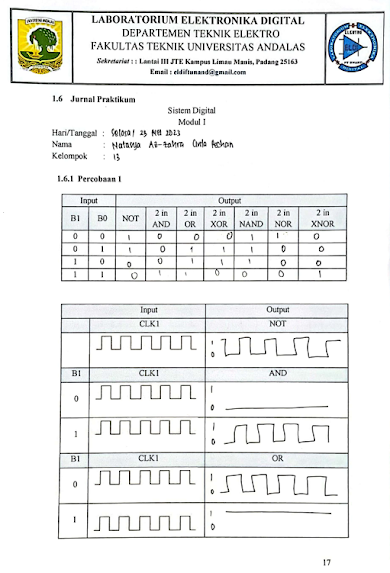

A. prosedur percobaan

1. Siapkan semua alat dan bahan yang diperlukan

2. Disarankan agar membaca datasheet setiap komponen

3. Rangkailah Rangkaian sesuai dengan gambar dibawah

4. Coba dijalankan rangkaian apabila ouput hidup/berputar (motor dc) maka rangkaian bisa digunakan

Komentar

Posting Komentar