Laporan Akhir Modul 2 Percobaan 2

1. Jurnal[Back]

2. Alat dan Bahan[Back]

1. IC 74LS112

2. Logic Probe

Logic Probe dijadikan sebagai hasil keluaran atau output

3.LED

LED merupakan singkatan dari Light Emitting Diode, merupakan salah satu perangkat semikonduktor yang mengeluarkan cahaya ketika arus listrik melewatinya, dan digunakan sebagai indikator keluaran (output).

4.SPDT

SPDT adalah singkatan dari Single Pole Double Throw. Switch jenis ini dapat menghubungkan dan memutuskan satu sambungan arus listrik pada dua arah sambungan.

5. Resistor

Resistor merupakan komponen elektronik yang memiliki dua pin dan didesain untuk mengatur tegangan listrik dan arus listrik.

3. Rangkaian Simulasi[Back]

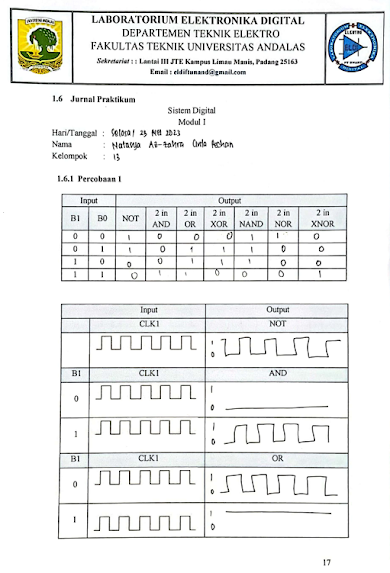

Percobaan 2 T flip-flop dan aplikasinya

1. Buatlah rangkaian seperti pada gambar 7. Hubungkan Output Q dan Q

dengan LED H7 & H6.

2. Buatlah kondisi Switch B0 s/d B4 seperti pada jurnal yang telah disediakan

dan catat kondisi logika LED H0 & H1 nya

Rangkaian pada proteus

4. Prinsip Kerja Rangkaian[Back]

Dapat dilihat pada jurnal praktikum pada percobaan 2, Untuk kondisi pertama, diketahui input T(B2) = dont care; PRE(B1) = 1; CLR(B0) = 0. Disini B2 terhubung dengan clock, B1 terhubung dengan S, dan B0 terhubung dengan R. Maka akan didapatkan output Q = 0; Q; = 1. Hal tersebut dikarenakan pin yang terdapat pada S dan R merupakan aktif low, dimana dia akan aktif saat berlogika 0. Dimana pada kondisi ini didapatkan nilai R berlogika 0, maka ia akan memaksa output atau Q untuk berlogika 0.

Untuk kondisi 2, diketahui input T(B2) = dont care; PRE(B1) = 0; CLR(B0) =1. Maka akan didapatkan output Q = 1; Q; = 0. Hal tersebut dikarenakan arus yang masuk pada set reset; S = 0; R = 1 dimana set reset merupakan aktif low yang mana akan aktif saat berlogika 0 maka dari itu set aktif dan akan memaksa nilai Q' untuk bernilai 0 atau saat reset tidak aktif, ia akan memaksa output untuk logika 1.

Untuk Kondisi 3, diketahui input T(B2) = dont care; PRE(B1) = 0; CLR(B0) =0. Maka akan didapatkan output Q = 1; Q; = 1. Hal tersebut dikarenakan pin set reset merupakan aktif low, dan akan memaksa output untuk berlogika 1. Disini akan terjadi kondisi terlarang atau keadaan yang tidak diperbolehkan.

Untuk Kondisi 4, diketahui input T(B2) = clock; PRE(B1) = 1; CLR(B0) =1. Maka akan didapatkan output Q = toggle; Q; = toggle. Hal tersebut dikarenakan output yang didapatkan akan berkebalikan secara terus-menerus.

5. Video Rangkaian[Back]

6. Analisa[Back]

Percobaan 2

1. Apa yang terjadi jika input T diberi logika nol atau low ?

Jawabannya:

Jika input T diberikan nilai 0 maka nilainya tidak akan berubah walaupun dipengaruhi oleh nilai clock tetapi jika T = 0 maka output tidak berubah.

2. Apa perbedaan ketika input clock D flip-flop diberi input risetime dan falltime ?

Jawabannya:

Ketika T flip-flop diberikan input clock risetime maka nilai T akan berubah setiap akan risetime sehingga nilai Q juga berubah begitupun sebaliknya pada keadaan falltime.

7. Link Download[Back]

Komentar

Posting Komentar