Laporan Akhir Modul 3 Percobaan 1

2. Alat dan Bahan

[Kembali]

1. IC 74LS112

2. Logic Probe

Logic Probe dijadikan sebagai hasil keluaran atau output

3. Rangkaian Simulasi

[Kembali]

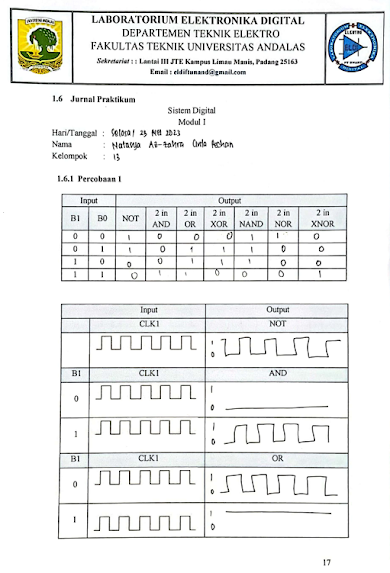

Percobaan 1 Asynchronous Binary Counter 4 bit dengan 4 J-K flip-flop.

1. Rangkai rangkaian seperti gambar dibawah ini.

Gambar Rangkaian percobaan Asynchronous Binary Counter 4 bit

2. Set Switch B0 ke logika 1, Analisa Output yang terjadi, operasi reset dapat

dilakukan setiap saat dengan menset Switch B0 ke logika 0. Gambarkan

bentuk sinyal CLK terhadap H0,H1,H2 dan H3, dan analisa hasil tersebut.

Rangkaian pada proteus

Gambar Rangkaian Sebelum Dijalankan

Gambar Rangkaian Setelah Dijalankan

4. Prinsip Kerja Rangkaian

[Kembali]

Pada percobaan 1 ini kita menggunakan clock berjenis falltime, yang mana clock akan mentrigger counter pada saat perpindahan output nilai dari 1 ke 0.

Pada percobaan 1 ini merupakan counter jenis asyncronous yang mana hanya flip flop paling ujung saja yang akan mendapatkan sinyal clock, sedangkan flip flop 2, 3, 4 mendapatkan sinyal clock dari output flip flop sebelumnya. Pada percobaan 1 menggunakan IC 74LS112 yang mana akan menghasilkan output 0 - 15, dimana jika dihubungkan dengan 7-segmen akan terlihat output 0-9 dan A-F. H0 akan mengeluarkan output ketika H0 menerima trigger pada saat terjadi falltime oleh clock, lalu untuk H1 akan mengeluarkan output ketika H1 menerima trigger pada saat terjadi falltime oleh H0, lalu untuk H2 akan mengeluarkan output ketika H2 menerima trigger pada saat terjadi falltime oleh H1, dan H3 akan mengeluarkan output ketika H3 menerima trigger pada saat terjadi falltime oleh H2, begitupun untuk H4 akan mengeluarkan output ketika H4 menerima trigger pada saat terjadi falltime oleh H3.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

Percobaan 1

1. Analisalah output yang dihasilkan pada percobaan 1 berdasarkan IC yang digunakan kapan H0, H1, H2, dan H3 mengeluarkan outputnya ?

Jawab:

Pada percobaan 1 merupakan counter jenis asyncronous yang mana hanya flip flop paling ujung saja yang akan mendapatkan sinyal clock, sedangkan flip flop 2, 3, 4 mendapatkan sinyal clock dari output flip flop sebelumnya. Pada percobaan 1 menggunakan IC 74LS112 yang mana akan menghasilkan output 0 - 15, dimana jika dihubungkan dengan 7-segmen akan terlihat output 0-9 dan A-F. H0 akan mengeluarkan output ketika H0 menerima trigger pada saat terjadi falltime oleh clock, lalu untuk H1 akan mengeluarkan output ketika H1 menerima trigger pada saat terjadi falltime oleh H0, lalu untuk H2 akan mengeluarkan output ketika H2 menerima trigger pada saat terjadi falltime oleh H1, dan H3 akan mengeluarkan output ketika H3 menerima trigger pada saat terjadi falltime oleh H2, begitupun untuk H4 akan mengeluarkan output ketika H4 menerima trigger pada saat terjadi falltime oleh H3.

2. Pada percobaan 1 menggunakan clock tipe falltime. Apakah ada pengaruh jika clocknya kita ubah ke tipe raisetime ? Jika iya, mengapa itu terjadi dan jika tidak kenapa demikian.

Jawab:

Pada percobaan 1 jika kita menggunakan clock tipe raisetime akan memberikan pengaruh terhadap outputnya. Outputnya akan berbeda dengan clock falltime dan clock raisetime hal tersebut dikarenakan clock akan memberikan trigger pada rangkaian pada kondisi yang berbeda. Pada clock tipe falltime, clock akan memberikan trigger pada saat rangkaian falltime sehingga terjadinya perubahan output ketika output sistem dari 1 ke 0. Sedangkan untuk raisetime akan terjadi perubahan output ketika output sistem dari 0 ke 1.

7. Link Download

[Kembali]

.png)

.jpeg)

Komentar

Posting Komentar