Laporan Akhir Modul 4 Percobaan 1

2. Alat dan Bahan

[Kembali]

1. IC 74111

2. Logic Probe

Logic Probe dijadikan sebagai hasil keluaran atau output

6. Gebang logika AND

Jika keluaran akan bernilai 1 jika semua nilai input adalah 1, dan jika salah satu atau lebih input ada yang bernilai nol maka output akan bernilai nol.

7. Gerbang logika NOT

Gerbang NOT sering juga disebut sebagai rangkaian inventer (pembalik). Tugas rangkaian NOT (pembalik) ialah memberikan suatu keluaran yang tidak sama dengan masukan.

3. Rangkaian Simulasi

[Kembali]

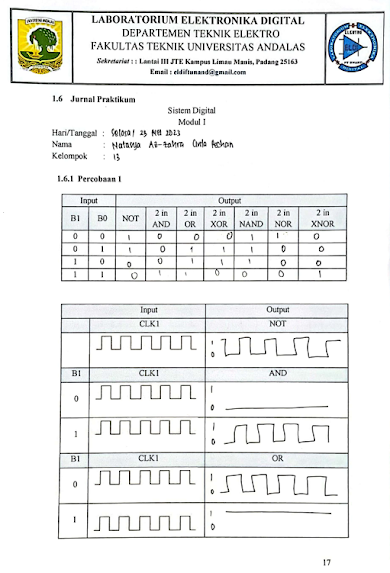

Percobaan 1 Serial In /Serial Out , Paralel In/Serial Out dan Paralel

In/Paralel Out Shift register dengan kapasitas 4 bit.

1. Matikan power supply modul.

2. Buatlah rangkaian seperti pada rangkaian percobaan dibawah ini.

Gambar Rangkaian percobaan Serial In /Serial Out , Paralel In/Serial Out dan

Paralel In/Paralel Out Shift register dengan kapasitas 4 bit.

Gambar Rangkaian Serial In /Serial Out , Paralel In/Serial Out dan Paralel

In/Paralel Out Shift register dengan kapasitas 4 bit.

3. Variasikan input switch sesuai dengan jurnal

4. Berikan keterangan pada jurnal sesuai output yang didapat

Rangkaian pada proteus

Gambar Rangkaian Sebelum Dijalankan

Gambar Rangkaian Setelah Dijalankan

4. Prinsip Kerja Rangkaian

[Kembali]

Untuk kondisi pertama didapatkan outputnya itu berupa shift register jenis Serial In Serial Out (SISO). Dimana pada saat B1 kita hidupkan atau kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara satu persatu dari shift register.

Untuk kondisi kedua, pada saat B1 kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, selanjutnya pada saat B2 kita beri trigger falltime kondisi ini bertujuan untuk mengambil data yang ingin kita masukkan, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara serentak dari shift register. Maka dari itu keadaan ini disebut Serial In Paralel Out (SIPO).

Untuk kondisi ketiga, B3 sampai B6 merupakan inputan dari datanya. Setelah kita mengatur dari inputannya, maka inputannya akan masuk secara serentak ke dalam shift register tersebut dan ketika data tersebut sudah masuk, maka data akan keluar dari shift register secara satu persatu. Maka dari itu kondisi ini disebut shift register jenis Paralel In Serial Out (PISO).

Untuk kondisi keempat, B3 sampai B6 merupakan inputan untuk kita mengatur datanya. Pada saat rangkaian dijalankan, data akan langsung masuk ke dalam shift register secara serentak dan akan keluar secara serentak juga dari shift register. Maka dari itu shift register disebut jenis Paralel In Paralel Out (PIPO).

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

Percobaan 1

1. Analisa output yang dihasilkan tiap-tiap kondisi

Jawab :

Untuk kondisi pertama didapatkan outputnya itu berupa shift register jenis Serial In Serial Out (SISO). Dimana pada saat B1 kita hidupkan atau kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara satu persatu dari shift register.

Untuk kondisi kedua, pada saat B1 kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, selanjutnya pada saat B2 kita beri trigger falltime kondisi ini bertujuan untuk mengambil data yang ingin kita masukkan, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara serentak dari shift register. Maka dari itu keadaan ini disebut Serial In Paralel Out (SIPO).

Untuk kondisi ketiga, B3 sampai B6 merupakan inputan dari datanya. Setelah kita mengatur dari inputannya, maka inputannya akan masuk secara serentak ke dalam shift register tersebut dan ketika data tersebut sudah masuk, maka data akan keluar dari shift register secara satu persatu. Maka dari itu kondisi ini disebut shift register jenis Paralel In Serial Out (PISO).

Untuk kondisi keempat, B3 sampai B6 merupakan inputan untuk kita mengatur datanya. Pada saat rangkaian dijalankan, data akan langsung masuk ke dalam shift register secara serentak dan akan keluar secara serentak juga dari shift register. Maka dari itu shift register disebut jenis Paralel In Paralel Out (PIPO).

2. Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip-flop, bandingkan output yang didapatkan

Jawab:

Setelah dilakukan perbandingan maka dapat disimpulkan output dan jenis shift register ada atau tanpa gerbang logika AND tetap sama. Karena pada saat ada gerbang AND nilai clock didapatkan dari clock dan B2 sedangkan tanpa adanya gerbang AND didapatkan dari clock. Kaki clock sama-sama mendapat trigger dari clock baik pada atau tidak adanya gerbang AND.

7. Link Download

[Kembali]

.png)

.jpeg)

Komentar

Posting Komentar